# Linear Power Amplifier Using Complementary HEXFETs<sup>®</sup> (HEXFET is the trademark for International Rectifier Power MOSFETs)

#### Topics covered:

A description of the circuit Performance Power supply requirements Set-up and troubleshooting Performance summary Related topics

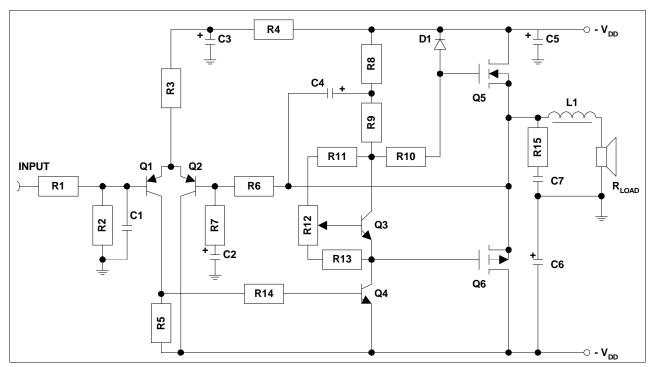

The class AB amplifier described in this application note uses a complementary pair of HEXFET Power MOSFET devices as the output stage. This feature offers performance improvements over the equivalent bipolar output stage and allows a reduction in the complexity of the driver circuit, the output devices being driven by a single class A driver. At the time the work was done, logic level HEXFET Power MOSFETs were not available and standard devices were used. The use of low-threshold devices would simplify the bias circuit and reduce the quiescent power dissipation The design described will deliver 60W rms into a 4 ohm load when working from +30V supplies. The bandwidth is in, excess of l00kHz, but may be tailored to the user requirements by making component value changes.

## 1. CIRCUIT DESCRIPTION

The amplifier circuit diagram is shown in Figure 1, and the components listing in Table 1. Split power supply rails ( $\pm V_{DD}$ ) are used, giving improved rejection of power supply ripple and allowing the load,  $R_{load}$ , to be direct coupled. The output devices  $Q_5$ ,  $Q_6$ , operate in source follower configuration. This offers a twofold advantage; a) the possibility of oscillation in the power output stage is reduced as the voltage gain is less than unity and b) signal feedback through the heatsink on which the devices are assembled is eliminated as the drain terminal, which is electrically connected to the tab on the TO220 package, is at dc voltage.

Symmetrical output is achieved by providing "bootstrapped" drive to the gate of the n-channel device,  $Q_5$ , from the output. The use of the bootstrap circuit,  $C_4$ ,  $R_8$ ,  $R_9$  also allows the driver transistor,  $Q_4$ , to operate at near constant current which improves the linearity of the driver stage. The diode  $D_1$  acts as a clamp for the bootstrap circuit, restricting the positive voltage at the gate of  $Q_5$  to  $+V_{DD}$ . This allows symmetry to be maintained under overload conditions.

Figure 1. Class AB Amplifier Circuit Diagram

Transistor  $Q_3$  and resistors  $R_{11}$ ,  $R_{12}$ ,  $R_{13}$  provide gate-source offset voltage for the output devices.  $R_{12}$  is variable, allowing adjustment of the output quiescent current for variation in HEXFET Power MOSFET threshold voltage. A degree of temperature compensation is built into the circuit as both the bipolar transistor,  $Q_3$ , emitter base voltage and the combined threshold voltages of the HEXFET Power MOSFETs,  $Q_5$ ,  $Q_6$  have a temperature coefficient of -0.3%/°C.

| Components List |                       |            |                        |                |                    |                 |                |  |

|-----------------|-----------------------|------------|------------------------|----------------|--------------------|-----------------|----------------|--|

| $R_1$           | 4.7ΚΩ                 | $R_9$      | 2.7ΚΩ                  | $C_1$          | 220 pF             | $Q_1$ , $Q_2$ , | 2N4356, 2N5086 |  |

| $R_2$           | $47 \mathrm{K}\Omega$ | $R_{10}$   | $680\Omega$            | $C_2$          | 100 μF 10V         |                 | or equivalent  |  |

| $R_3$           | $15$ K $\Omega$       | $R_{11}$   | $10 \mathrm{K}\Omega$  | $C_3$          | $47  \mu F  40V$   | $Q_3$ , $Q_4$ , | 2N4410, 2N5088 |  |

| $R_4$           | $1.2$ K $\Omega$      | $R_{12}$   | $1$ K $\Omega$ Pot.    | $C_4$          | $47  \mu F  40V$   |                 | or equivalent  |  |

| $R_5$           | $560\Omega$           | $R_{13}$   | $820\Omega$            | $C_5$          | $2200  \mu F  40V$ | $Q_5$           | IRF532         |  |

| $R_6$           | $47 \mathrm{K}\Omega$ | $R_{14}$   | $4.7 \mathrm{K}\Omega$ | $C_6$          | $2200  \mu F  40V$ | $Q_6$           | IRF9532        |  |

| $R_7$           | $4.70\Omega$          | $R_{15}$   | $10 \Omega 1 W$        | $\mathbf{C}_7$ | 68 nF              | $\mathbf{D}_1$  | IN4002         |  |

| $R_8$           | $2.7$ K $\Omega$      | $R_{load}$ | $8/4~\Omega$           | $L_1$          | 3 μH aircored      |                 |                |  |

Table 1. Components List

The class A driver transistor, Q<sub>4</sub>, operates at a bias current determined by resistors R<sub>8</sub>, R<sub>9</sub>, nominally 5mA. Q<sub>4</sub> is driven by a PNP differential

input pair, Q1, Q2. The bias current in the input stage is set to 2mA by resistor R<sub>3</sub>. Negative feedback from the output of the amplifier is fed to the base of Q<sub>2</sub> by resistor R<sub>6</sub>. Components R<sub>7</sub>, C<sub>2</sub> set the closed loop gain of the amplifier  $(R_6/R_7)$  and provide low frequency gain boosting. The additional components R<sub>15</sub>, C<sub>7</sub> connected between the output node and ground suppress the high frequency response of the output stage, allowing the h.f. performance of the amplifier to be determined by the input circuit. Components R<sub>1</sub>, R<sub>2</sub>,  $C_1$  at the input of the amplifier define the input impedance (47Kohm) and suppress noise.

The amplifier input stage requires additional power supply ripple suppression which is provided by components R<sub>4</sub>, C<sub>3</sub>.

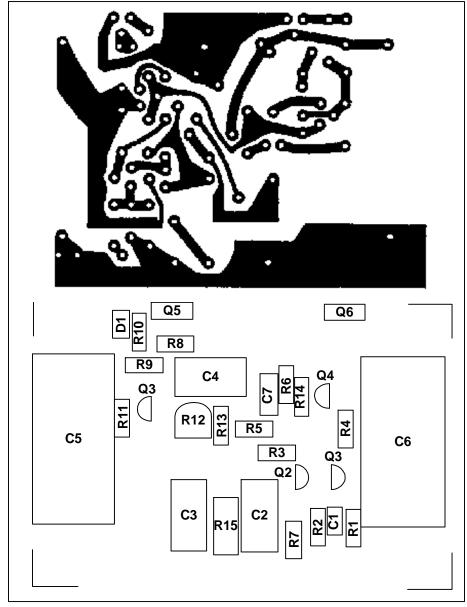

Additional circuit components have been added to ensure high frequency stability of the complete amplifier. Placement of the components and component values will depend to some extent on the printed circuit board layout. The following rules should be followed when designing the printed circuit board:

(a) A 'common ground' principle should be

Figure 2. Amplifier Printed Circuit Board Layout

adopted, i.e., power supply decoupling capacitors, load and input stage biasing components should all be taken to ground in close proximity, eliminating the effects of common node ground current. Similarly, a "common output node" should be used, the load, feedback resistor and h.f. suppression components being taken from a common point on the pcb.

- (b) The length of connecting lead to the gate terminals of HEXFET Power MOSFETs  $Q_5$ ,  $Q_6$  should be an absolute minimum to avoid oscillation of the power output stage. A series gate resistor,  $R_{10}$ , may be used to suppress oscillation, but too high a resistor value will limit the slew rate. Oscillation of the amplifier caused by capacitive coupling to the base of the driver transistor,  $Q_4$ , is suppressed by the addition of a series resistor,  $R_{14}$ .

- (c) Phase shift in the amplifier when driving a reactive load can lead to high frequency instability. With a capacitive load, the addition of a small, air-cored choke ( $3\mu H$  with an 8 ohm,  $2\mu F$  load) will restore stability. The final value of the choke is defined by experiment.

Figure 2 shows a printed circuit layout which can be used for the circuit shown in Figure 1. The preceding design rules have been followed.

### 2. AMPLIFIER PERFORMANCE

(a) *Output Power:* To achieve 60W rms into a 4 ohm load, the current in the load is 3.9A rms or 5.5A pk. This information is derived from equations (1) and (2):

$$P_{O} = I_{rms}^{2} R_{load}$$

$$= \frac{V_{rms}^{2}}{R_{load}}$$

(1)

$$I_{rms} = \frac{I_{pk}}{\sqrt{2}}$$

(2)

$$V_{\rm rms} = \frac{V_{\rm pk}}{\sqrt{2}} \tag{3}$$

Also from equation (1), the voltage developed across the load at 60W output is 15.5V rms or 22V pk. To sustain a source current of 5.5A, the n-channel HEXFET Power MOSFET, IRF530, requires a gate-source voltage of 5V. One can conclude that the gate bias voltage to achieve peak power in the positive sense is  $V_{pk} + V_p = 27V$ . A similar calculation for the negative peak, using the P channel HEXFET Power MOSFET IRF9530, shows that a negative gate bias supply of -28V is required.

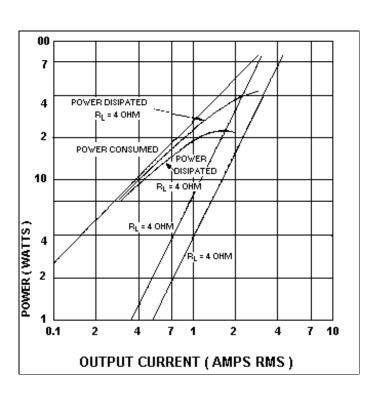

Consequently, a ±30V supply will be adequate for a 60W output, provided that the supply voltage does not fall below ±28V when loaded, i.e., the power supply impedance should be better than 1 ohm. The relationship between the power delivered to the load and the power absorbed from the supply is shown in Figure 3, assuming a sinusoidal waveform and a ±30V supply. The curve representing the power delivered to the load can be easily plotted with the help of equation (1) for different values of load current.

**Figure 3.** Power Curves for the Amplifier with 4 and 8 Ohm Loads and  $\pm$  30V Power Suuplies

The power absorbed from the supply has been plotted with the help of the following relationship:

$$P_{S} = (V_{avg})(I_{avg})$$

$$= (2V_{DC})(\frac{\sqrt{2}}{\pi}I_{rms})$$

(4)

The difference between the two is the power dissipated in the HEXFET Power MOSFETs and as it can be seen from Figure 3, it has a peak of approximately 46W. Assuming a maximum ambient temperature of 55°C, the total thermal resistance between the junction of the two HEXFET Power MOSFETs and the ambient will have to be less than 2°C/W. Considering that the IRF530 and IRF9530 have a thermal resistance between junction and case of 1.7°C/W each, the maximum case temperature will have to be less than 110°C and the thermal resistance of the heatsink will have to be less than 1.15°C/W to ambient.

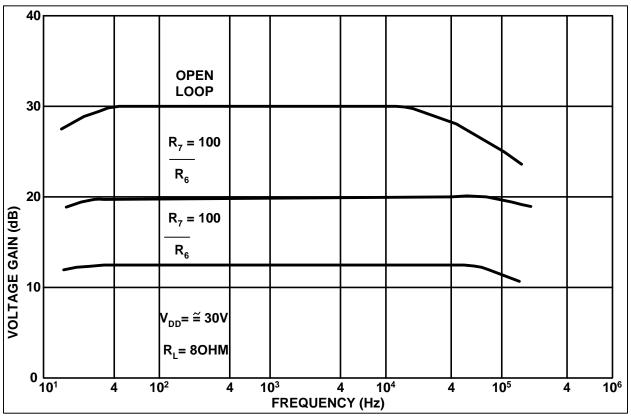

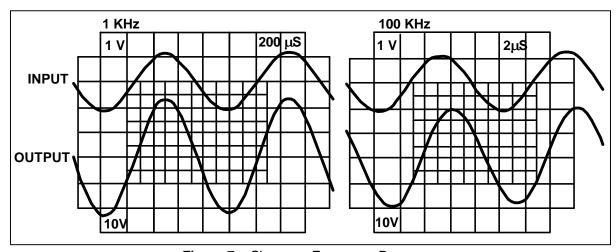

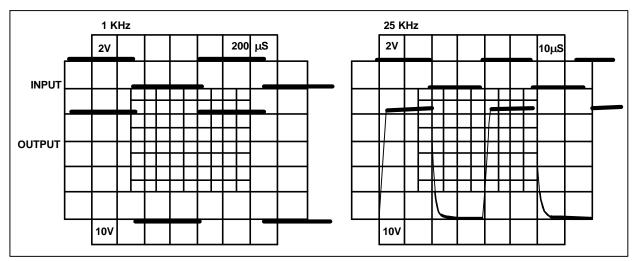

(b) Frequency Response: Open shown in Figure 4. The open loop gain, measured with gate and source connections to the HEXFET Power MOSFETs broken, is 30db, -3db points occurring at 15 Hz and 60kHz. Closed loop curves are shown for amplifier gains of 100 ( $R_7 = 470$  ohm) and 20 ( $R_7 = 2.2K$  ohm). In both instances the curves remain flat to within +1db between 15 Hz and 100kHz with an 8 ohm load. The slew rate of the amplifier, measured with a 2V pk-pk square wave input is  $13V/\mu s$  positive going and  $16V/\mu s$  negative going. The discrepancy could be balanced out by addition of a series gate resistor for  $Q_6$ .

Figure 4. Amplifier Open and Closed Loop Frequency Response Curves

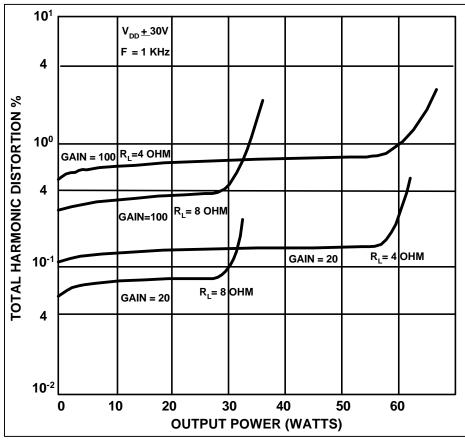

- (c) *Total Harmonic Distortion*: The fidelity of the amplifier is shown in the distortion curves, Figure 5, and is limited by the loop gain. Reduction of the closed loop gain from 100 to 20 produces a significant improvement in distortion figure. The output stage quiescent current was adjusted to 100mA and can influence the distortion measurement significantly if allowed to fall below 50mA.

- (d) Quiescent Operating: The dependence of the quiescent current in the output stage and of the offset voltage on power supply voltage are illustrated in Table 2. The quiescent current is set by first adjusting the potentiometer,  $R_{12}$ , for minimum offset voltage-turned fully anticlockwise if the pcb layout in Figure 2 is used and applying the power supply voltage, the positive

supply passing through an ammeter with 1A f.s.d.  $R_{12}$  is then adjusted until the meter reading is 100mA with  $\pm 30$ V supplies. The meter should be removed from circuit before applying an input signal to the amplifier.

# 3. POWER SUPPLY REGULATION REQUIREMENTS

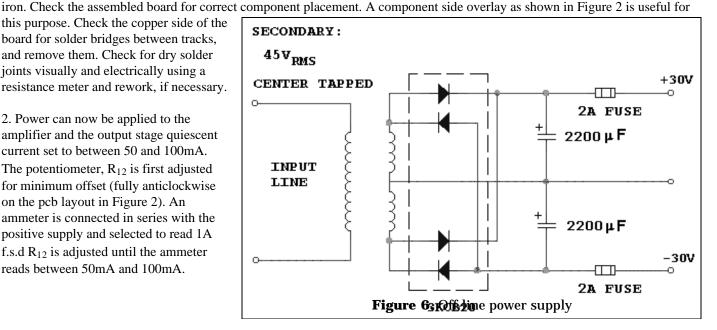

A simple line derived power suitable for the class AB amplifier is illustrated in Figure 6. The ±30V supplies are taken from the centertapped secondary of the line transformer. The 2200µF decoupling capacitors, (Figure 1) which should be mounted as close as possible to the amplifier output stage, reduce the supply frequency ripple to 5.5V pk-pk at full load.

## 4. SET-UP PROCEDURE AND TROUBLESHOOTING

It is unlikely that any experienced experimenter will have difficulty in achieving satisfactory results when building an amplifier to this design. The printed circuit board shown in Figure 2 is intended to assist in this respect. The major problems anticipated are those associated with the faulty assembly of components and damage to the HEXFET Power MOSFETs through handling or circuit oscillation.

The following troubleshooting checklist is offered as a guide to the experimenter:

1. When assembling the printed circuit board, mount the passive components first, ensuring the correct polarity of electrolytic capacitors. Then solder in the transistors Q1 - Q4 checking for correct pin identification. Finally, mount the HEXFET Power MOSFETs, avoiding static discharge by shorting the pins together to ground and using a grounded soldering

this purpose. Check the copper side of the board for solder bridges between tracks, and remove them. Check for dry solder joints visually and electrically using a resistance meter and rework, if necessary.

2. Power can now be applied to the amplifier and the output stage quiescent current set to between 50 and 100mA. The potentiometer,  $R_{12}$  is first adjusted for minimum offset (fully anticlockwise on the pcb layout in Figure 2). An ammeter is connected in series with the positive supply and selected to read 1A f.s.d R<sub>12</sub> is adjusted until the ammeter reads between 50mA and 100mA.

Figure 5. Amplifier Total Harmonic Distortion Curves

Quiescent current setting can be performed without the load connected.

If, however, a loudspeaker load is connected in circuit, it can be protected by a fuse from dc overload. With the quiescent current set, the output offset voltage can be confirmed to be less than 100mV. Excessive and erratic variation in quiescent current as R<sub>12</sub> is adjusted are indicative of circuit oscillation or faulty wiring. The solutions described in "Circuit Description" (series gate resistors, minimized gate wiring and common earthing) should be adopted. Also, supply decoupling capacitors should be mounted in close proximity to the amplifier output stage and load ground point. Quiescent current setting should be performed with the HEXFET Power MOSFETs mounted on their heatsink to avoid overdissipation.

3. With the quiescent current set, the ammeter should be removed from the positive supply and a signal can be applied to the amplifier input. Signal requirements for full rated output are:

```

\begin{split} & \text{gain} = 100: \\ & R_L = 4~\Omega,~V_{\text{in}} = 150 \text{mV rms} \\ & R_L = 8~\Omega,~V_{\text{in}} = 160 \text{mV rms} \\ & \text{gain} = 20: \\ & R_L = 4~\Omega,~V_{\text{in}} = 770 \text{mV rms} \\ & R_L = 8~\Omega,~V_{\text{in}} = 800 \text{mV rms} \end{split}

```

| Variation in Output Offset Voltage and Output Quiescent Current with Supply Voltage |                      |                                 |  |  |  |  |  |

|-------------------------------------------------------------------------------------|----------------------|---------------------------------|--|--|--|--|--|

| Supply Voltage                                                                      | Output Offset        | <b>Output Quiescent Current</b> |  |  |  |  |  |

| $+$ $\mathbf{V_{DD}}$ $\mathbf{V}$                                                  | $\mathbf{V_{OS}}$ mV | Iq mA                           |  |  |  |  |  |

| 35                                                                                  | -40                  | 135                             |  |  |  |  |  |

| 30                                                                                  | -20                  | 100                             |  |  |  |  |  |

| 25                                                                                  | +4                   | 75                              |  |  |  |  |  |

| 20                                                                                  | +30                  | 54                              |  |  |  |  |  |

Table 2. Variation in Output offset voltage and Output quiescent current with supply voltage

"Clipping" of the output waveform when operating at rated power indicates poor supply regulation and can be remedied by reducing the input signal amplitude and derating the amplifier. Alternatively, a lower impedance supply should be used. The frequency response of the amplifier can be checked over the frequency range 15 Hz - 100 kHz with the aid of an audio test set or signal generator and oscilloscope. Distortion of the output waveform at high frequency is indicative of a reactive load and adjustment of the output choke will be required to restore the waveform. The high frequency response may be tailored with a compensation capacitor in parallel with  $R_6$ . The low frequency response is controlled by components  $R_7$ ,  $C_2$ .

- 4. Hum pickup will be more likely to occur in a high gain circuit. Pickup at the high impedance input is minimized by use of a shielded cable, grounded at the signal source. Supply frequency ripple injected through the supply to the input stage of the amplifier can be detected across capacitor,  $C_3$ . This is attenuated by the common mode rejection ratio of  $Q_1$ ,  $Q_2$  before being amplified. However, if this is the source of hum, adjustment to the values of  $C_3$ ,  $R_5$  can be made to suppress the signal amplitude.

- 5. In the event of the output stage being destroyed, either through short circuit load or h.f. oscillation, both HEXFET Power MOSFETs should be replaced. It is unlikely, however, that other circuit components will have been affected. The setup procedure should, of course, be repeated with the new devices in circuit.

## 5. PERFORMANCE SUMMARY

Using a complementary pair of HEXFET Power MOSFETs, IRF530 and IRF9530 and with a ±30V supply, the following performance can be achieved:

Maximum rms output power:

60W into  $4\Omega$  32W into  $8\Omega$

Bandwidth:

15 Hz to 100kHz ±1db

Total harmonic distortion (1kHz):

0.15% at 60W into  $4\Omega$  0.08% at 32W into  $8\Omega$

Voltage gain:

Adjustable, X100 to X20

Input impedance:  $47K\Omega$

Figure 7a: Sinewave Frequency Response

Figure 7b: Square Wave Response

Figure 7a & 7b: Amplifier Waveforms illustrating Frequency Response

Figure 7 illustrates the amplifier response to 1kHz and 100kHz sinewave input signals and also the square wave response at 1kHz and 25kHz.

### Related topics:

P-Channel HEXFET Power MOSFETs Gate drive requirements

IR FAR EAST: K&H Bldg., 2F, 3-30-4 Nishi-Ikeburo 3-Chrome, Toshima-Ki, Tokyo Japan 171 Tel: 81 3 3983 0086

**IR SOUTHEAST ASIA:** 315 Outram Road, #10-02 Tan Boon Liat Building, Singapore 0316 Tel: 65 221 8371 Data and specification subject to change without notice.